- 您现在的位置:买卖IC网 > Sheet目录320 > DK-DEV-5AGXB3N/ES (Altera)ARRIA V DEVELOPMENT KIT

�� �

�

�

�AV-51001�

�2013.12.26�

�Enhanced� Configuration� and� Configuration� via� Protocol�

�35�

�Apart� from� lowering� cost� and� power� consumption,� partial� reconfiguration� increases� the� effective� logic� density�

�of� the� device� because� placing� device� functions� that� do� not� operate� simultaneously� is� not� necessary.� Instead,�

�you� can� store� these� functions� in� external� memory� and� load� them� whenever� the� functions� are� required.� This�

�capability� reduces� the� size� of� the� device� because� it� allows� multiple� applications� on� a� single� device� —� saving�

�the� board� space� and� reducing� the� power� consumption.�

�Altera� simplifies� the� time-intensive� task� of� partial� reconfiguration� by� building� this� capability� on� top� of� the�

�proven� incremental� compile� and� design� flow� in� the� Quartus� II� design� software.� With� the� Altera� solution,�

�you� do� not� need� to� know� all� the� intricate� device� architecture� details� to� perform� a� partial� reconfiguration.�

�Partial� reconfiguration� is� supported� through� the� FPP� x16� configuration� interface.� You� can� seamlessly� use�

�partial� reconfiguration� in� tandem� with� dynamic� reconfiguration� to� enable� simultaneous� partial� reconfiguration�

�of� both� the� device� core� and� transceivers.�

�Enhanced� Configuration� and� Configuration� via� Protocol�

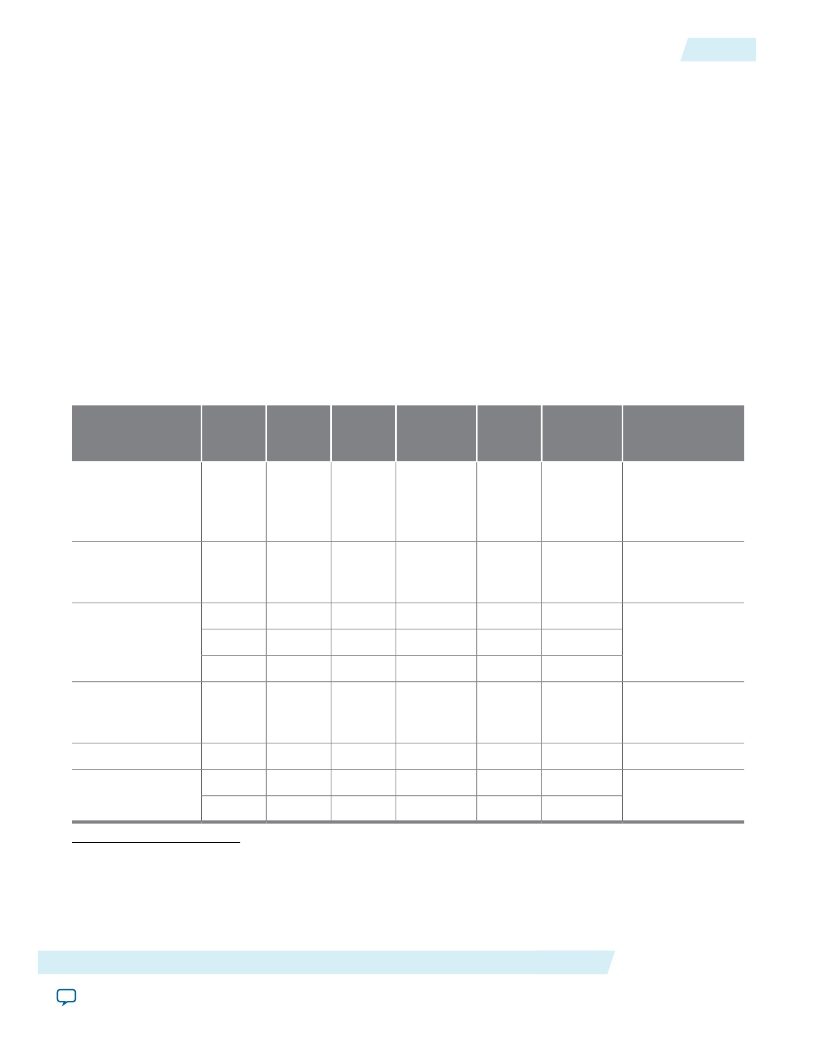

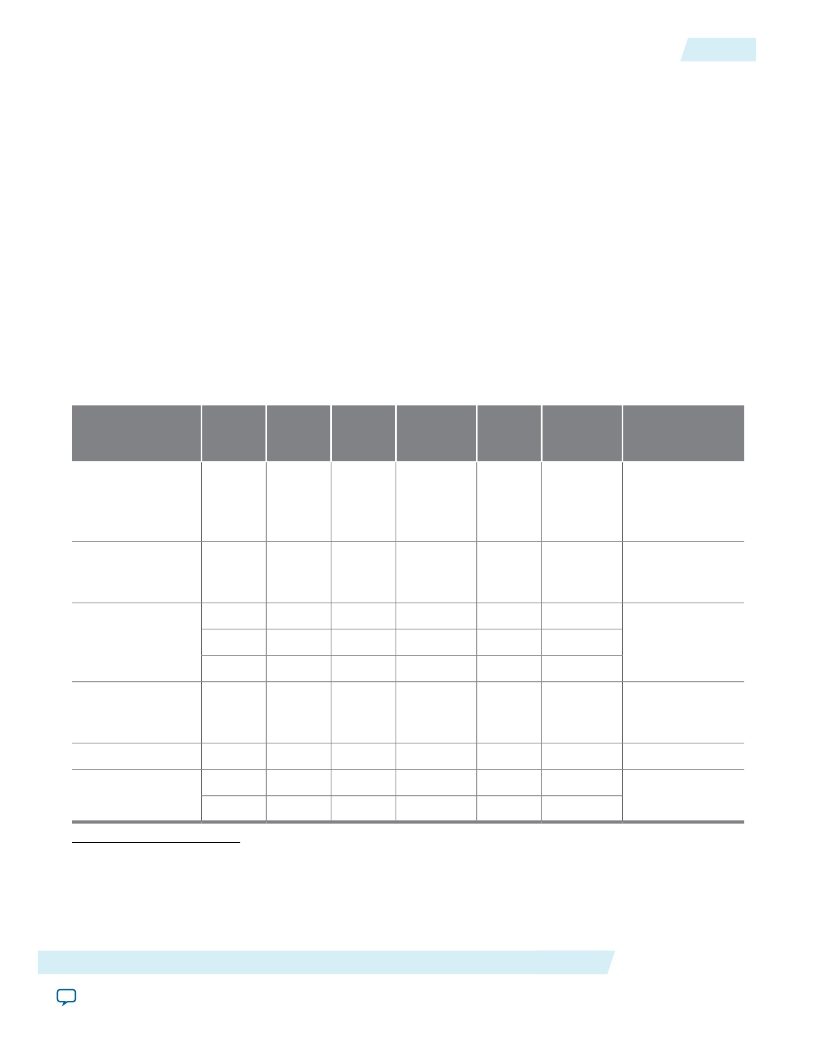

�Table� 23:� Configuration� Modes� and� Features� of� Arria� V� Devices�

�Arria� V� devices� support� 1.8� V,� 2.5� V,� 3.0� V,� and� 3.3� V� (20)� programming� voltages� and� several� configuration� modes.�

�Reconfiguration�

�Mode�

�Data�

�Width�

�Max� Clock� Max� Data� Decompression�

�Rate� Rate�

�Design�

�Security�

�Partial�

�(21)�

�Remote� System�

�Update�

�(MHz)�

�(Mbps)�

�AS� through� the�

�1� bit,� 4�

�100�

�—�

�Yes�

�Yes�

�—�

�Yes�

�EPCS� and� EPCQ�

�serial� configura-�

�tion� device�

�bits�

�PS� through� CPLD�

�1� bit�

�125�

�125�

�Yes�

�Yes�

�—�

�—�

�or� external�

�microcontroller�

�8� bits�

�125�

�—�

�Yes�

�Yes�

�—�

�FPP�

�CvP� (PCIe)�

�16� bits�

�(23)�

�32� bits�

�x1,� x2,� x4,�

�125�

�100�

�—�

�—�

�—�

�—�

�Yes�

�Yes�

�Yes�

�Yes�

�Yes�

�Yes�

�Yes� (22)�

�—�

�Yes�

�Parallel� flash� loader�

�—�

�and� x8�

�lanes�

�JTAG�

�Configuration� via�

�HPS�

�1� bit�

�16� bits�

�32� bits�

�33�

�125�

�100�

�33�

�—�

�—�

�—�

�Yes�

�Yes�

�—�

�Yes�

�Yes�

�—�

�Yes� (22)�

�—�

�—�

�Parallel� flash� loader�

�(20)�

�(21)�

�(22)�

�(23)�

�Arria� V� GZ� does� not� support� 3.3� V.�

�Partial� reconfiguration� is� an� advanced� feature� of� the� device� family.� If� you� are� interested� in� using� partial�

�reconfiguration,� contact� Altera� for� support.�

�Supported� at� a� clock� rate� of� 50-62.5� MHz.�

�Arria� V� GZ� only�

�Arria� V� Device� Overview�

�Send� Feedback�

�Altera� Corporation�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

DK-DEV-5M570ZN

KIT DEV MAX V 5M570Z

DK-DEV-5SGXEA7N

KIT DEV STRATIX V FPGA 5SGXEA7

DK-DSP-2S180N

DSP PRO KIT W/SII EP2S180N

DK-DSP-3C120N

KIT DEV DSP CYCLONE III EDITION

DK-K7-CONN-CES-G

KINTEX-7 FPGA CONNECTIVITY KIT

DK-K7-EMBD-CES-G-J

KINTEX-7 FPGA EMBEDDED KIT JAPAN

DK-MAXII-1270N

KIT DEV MAXII W/EPM 1270N

DK-N2EVAL-3C25N

KIT DEV NIOS II CYCLONE III ED.

相关代理商/技术参数

DK-DEV-5ASTD5N

功能描述:KIT DEV ARRIA V FPGA 制造商:altera 系列:Arria V ST 零件状态:在售 类型:FPGA 配套使用产品/相关产品:Arria? V ST 内容:板 标准包装:1

DK-DEV-5CEA7N

功能描述:可编程逻辑 IC 开发工具 FPGA Development Kit For 5CEFA7F31C7N

RoHS:否 制造商:Altera Corporation 产品:Development Kits 类型:FPGA 工具用于评估:5CEFA7F3 接口类型: 工作电源电压:

DK-DEV-5CEA7N/P

制造商:Altera Corporation 功能描述:Cyclone VE Devkit Promotional 制造商:Altera 功能描述:Cyclone VE Devkit Promotional

DK-DEV-5CEA7NES

功能描述:可编程逻辑 IC 开发工具 FPGA Development Kit For 5CEFA7F3

RoHS:否 制造商:Altera Corporation 产品:Development Kits 类型:FPGA 工具用于评估:5CEFA7F3 接口类型: 工作电源电压:

DK-DEV-5CEA7NESP

制造商:Altera Corporation 功能描述:KIT DEVELOPMENT CYCLONE V E

DK-DEV-5CEA7NP

制造商:Altera Corporation 功能描述:Cyclone VE Devkit Promotional 制造商:Altera 功能描述:Cyclone VE Devkit Promotional

DK-DEV-5CGTD9N

功能描述:可编程逻辑 IC 开发工具 FPGA Development Kit For 5CGTFD9E5F35

RoHS:否 制造商:Altera Corporation 产品:Development Kits 类型:FPGA 工具用于评估:5CEFA7F3 接口类型: 工作电源电压:

DK-DEV-5CGXC7NES

功能描述:可编程逻辑 IC 开发工具 FPGA Development Kit For 5CGXFC7D6F31C7N

RoHS:否 制造商:Altera Corporation 产品:Development Kits 类型:FPGA 工具用于评估:5CEFA7F3 接口类型: 工作电源电压: